- Introducción

- Esquema memoria RAM Timex FDD

- Reemplazo ULA 1H35 y memoria RAM

- Diseño placas para memoria RAM estática

- Ficheros

- Link

Introducción

Ha llegado a mis manos un par de interfaces Timex FDD para su reparación. En concreto se trata de un FDD3 y un FDD3000.

|

|

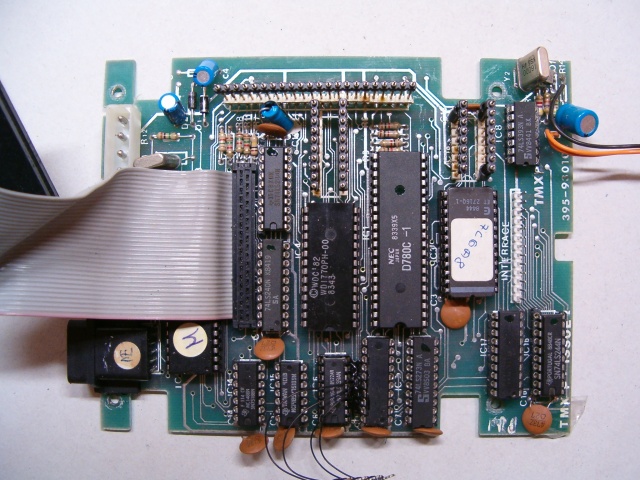

| FDD 3 | FDD3000 |

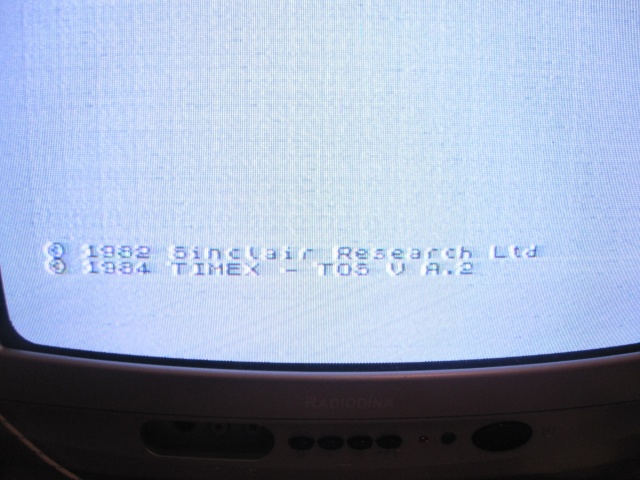

El fallo en ambos sistemas era similar. El FDD trata de leer el disco del sistema operativo TOS y tras unos segundos se para.

Este interface es bastante complicado de reparar debido a que se trata de un sistema con su propio microprocesador z-80, memoria ROM, RAM, puertos RS232 y un puerto paralelo para comunicarse con el Timex o Spectrum al que está conectado.

Después de algún tiempo comprendiendo como funciona un FDD y tras múltiples pruebas, encontré la razón del fallo de ambos sistemas. La memoria RAM no funcionaba bien.

El Timex FDD funciona de una manera curiosa. Al arrancar, el z-80 lee la ROM donde sólo se almacena una pequeña rutina de 128 bytes. Esta rutina permite al z-80 comunicarse con el WD1770 y pedirle que lea las 3 primeras pistas del disco.

Cuando lee las pistas, se desactiva la ROM y vuelca el contenido del disco TOS a la memoria RAM, que está activada desde la posición 0000h.

Esto explica el fallo de las 2 unidades Timex. Al no funcionar correctamente la memoria RAM, el sistema lee las pistas pero no puede continuar.

En uno de los casos, la controladora tenía una memoria RAM compuesta por 8 chip 4116 (16K) y tenía un chip estropeado. Se cambio el chip y quedo arreglado el interface.

El problema llegó con la otra controladora. Esta disponía de 8 chip RAM 4264 dispuestos de tal manera que daba 64K RAM al sistema. Sin embargo, el problema estaba en el controlador de memoria RAM que llevan los FDD. Se trata de un chip FERRANTI ULA 1H35 del que no hay información y del que no hay repuesto.

Esquema memoria RAM Timex FDD

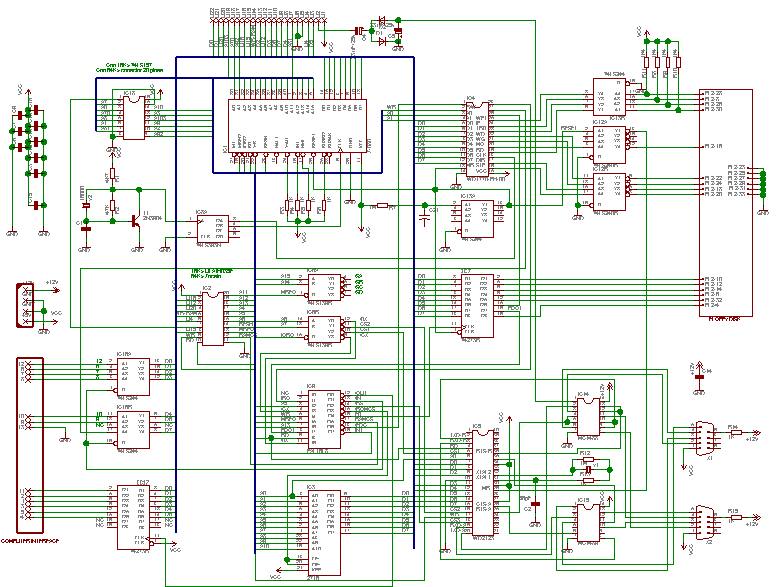

El esquema de la controladora FDD es el siguiente:

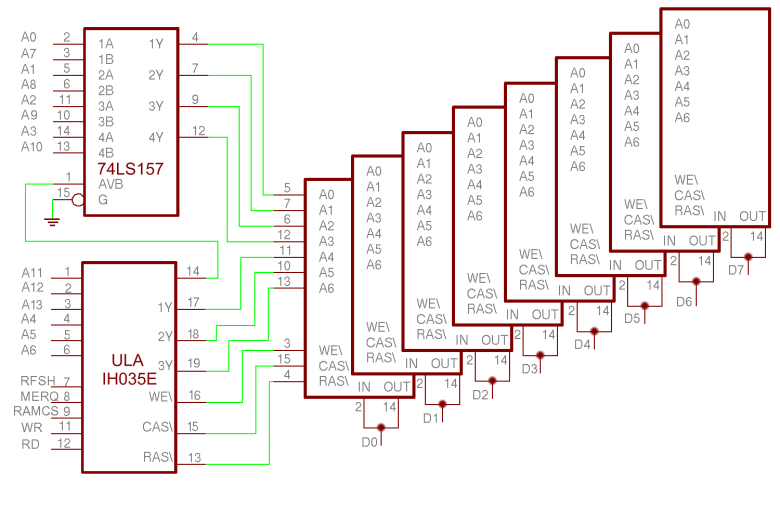

La memoria RAM va en una placa aparte. El esquema de memoria más simple es el de 16K.

La ULA tiene 2 partes diferenciadas. Por un lado, complementa al 74LS157 en multiplexar el bus de direcciones (pines 17,18 y 19) y por el otro lado se encarga de generar las señales CAS (15), RAS(13) y WRITE(16) y Enable 74LS157(14).

Una señal muy importante de entrada es RAMCS, que viene de la PAL16L8. Esta PAL controla la activación de la ROM y de la RAM. La ULA no interviene en este proceso.

Reemplazo ULA 1H35 y memoria RAM

Una opción para reparar el FDD con la ULA estropeada sería sintetizar el funcionamiento de la ULA. La parte del multiplexado es fácil, pues se trataría de un 74LS157 adicional. Para la parte de las señales CAS,RAS, WRITE se podría investigar en los circuitos con componentes discretos de otros ordenadores como el que lleva el spectrum.

La mejor opción es partir de este esquema que podemos encontrar en esta pagina web. Como se puede ver, este esquema de FDD no tiene ULA y lo sustituye por un chip 74LS00, un 74LS02, un 74LS74 y un 74LS157.

Sin embargo, mi opción ha sido distinta. La ULA estaba rota, no tenía chips RAM 4264,¿Y si cambiase toda la RAM dinámica por RAM estática?

En la actualidad se pueden encontrar chips de RAM estática de 32K, 128K, 512K. Con un solo chip se podría sustituir todas la RAM vieja y eliminar también la ULA.

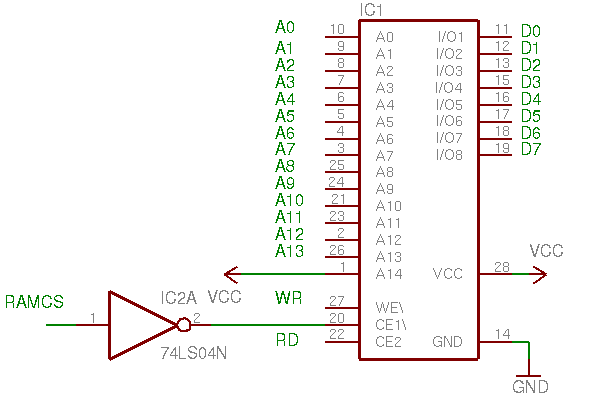

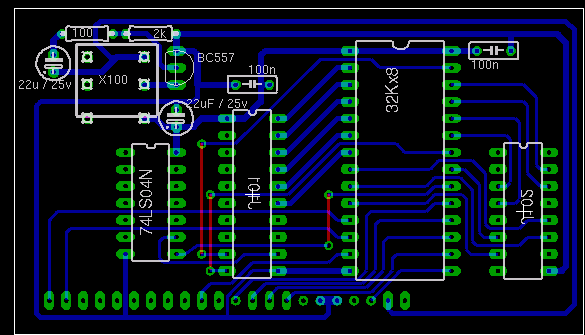

El esquema básico utilizando RAM estática es el siguiente:

Este esquema utiliza una memoria de 32K donde sólo se utilizan 16K. Si quisieramos 64K, tendríamos que usar un chip de 128K o 512K y añadir las señales A14 y A15.

La puerta 74LS04 hay que incluirla. No está en la placa original.

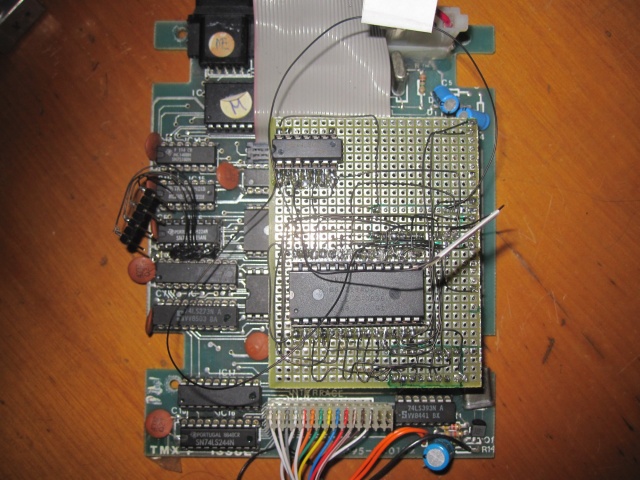

Para probar este diseño, se hizo un diseño real con placa perforada sobre la controladora estropeada.

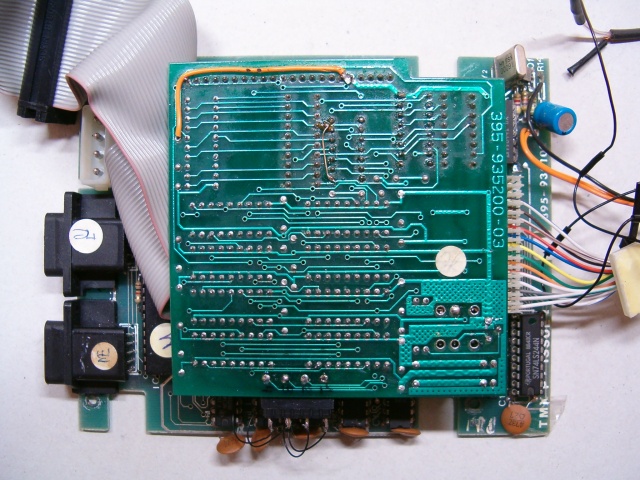

Foto controladora FDD3000 con placa 64K de RAM.

Si quitamos la placa donde está la RAM, podemos ver la placa principal.

Al ser el modelo con 64K, el 74LS157 y la ULA no están en la controladora sino en la placa donde está la memoria. En su lugar hay una tira de pines que suben las señales hacia la placa de RAM. Esto nos facilita el trabajo a la hora de crear la placa de pruebas porque de estas tiras de pines podemos sacar el bus de direcciones A0..A13, RD, WR y RAMCS. Del conector de 22 pines superior, sólo podemos sacar las señales del bus de datos (D0..D7).

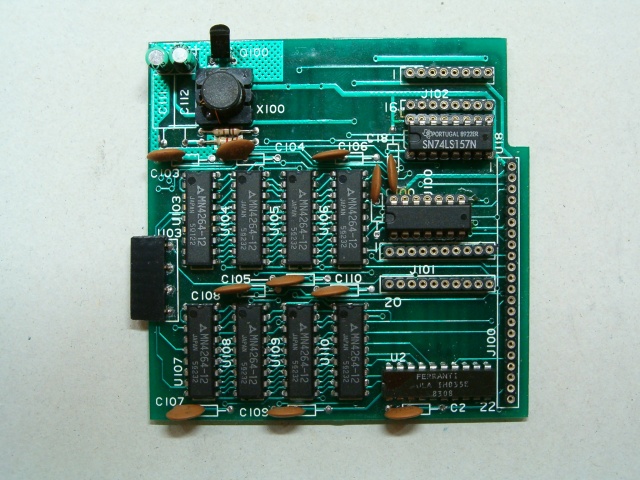

La placa de RAM tiene el siguiente aspecto:

La parte RAM está compuesta por los 8 4264, el 74LS157 y un 74LS32 (que sirve para direccionar más de 16K).También hay un pequeño convertidor DC-DC para sacar -12v necesarios para el MC1488 de los puertos RS-232 que lleva la placa principal.

La controladora con la placa de pruebas nos queda así.No he puesto el circuito de -12v porque solo se usa para los puertos RS-232:

Y el resultado final es el siguiente:

Diseño placas para memoria RAM estática

Los siguientes diseños no se han probado en la realidad. Las señales de los buses de datos y direcciones tiene señales cambiadas para simplificar el diseño de la placa. Las placas están diseñadas como la original, los componentes van enfrentados a los de la controladora y nosotros veríamos la cara de las pistas.

Placa con 16K.

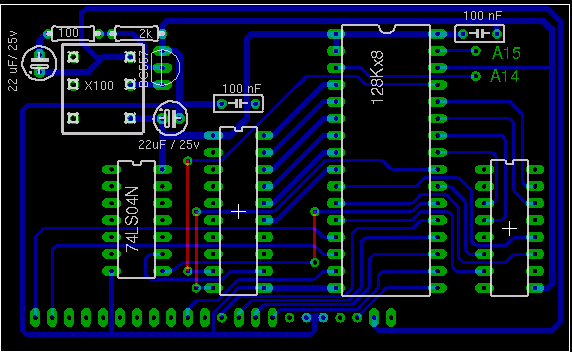

Placa con 64K.

Esta placa precisaría 2 uniones extra contra la placa principal. Las señales A14 y A15 no están presente en ninguno de los conectores. La memoria RAM a utilizar sería una 128Kx8 o 512Kx8.

Ficheros

- Ficheros Eagle de las placa prototipo.

- Esquemas FDD3000, placa principal, memoria 16k y 64k original.

Links

- Página web con información de los Timex FDD3000 y FDD3

- Pagina con mucha información de los Timex

- Mi página con los esquemas, placas, ficheros Eagle y algunas fotos más

2011. Artículo escrito por José Leandro Novellón.