Super cartucho INTERFACE 2

Diseño con GAL

El diseño con TTL es muy sencillo pero algo

aparatoso. La placa no es muy pequeña y tiene bastante pistas.

Para reducir todo el diseño hay que recurrir a chip como las PAL

o GAL.

¿Que es una GAL? Una GAL es un chip que tiene

en su interior muchas puertas que pueden ser interconectadas para

formar funciones complejas. Estos chip son la evolución de los

chip PAL. Se diferencian básicamente en la tecnología de

fabricación ( TTL las PAL y CMOS las GAL) y en las

conexiones ( fijas en las PAL y borrables eléctricamente

en las GAL). Las GAL han evolucionado a nuevas familias mucho

más complejas y potentes.

Gracias a chips como este, se puede reducir todos

los chip empleando en el diseño con TTL por una sola GAL.

Sin embargo no todo es color de rosa. El uso de

estos chip requieren un programador específico además de

software

para crear las funciones y los ficheros de fusibles ( para crear las

conexiones) que suele estar fuera del alcance de un aficionado a

la electrónica. Por suerte es posible encontrar por la red un

par de programadores "caseros ".

GALBLAST

( El que me he construido )

EML

En cuanto al software he encontrado los

siguientes programas

PALASM

OPALJR

Este software es ' libre ' porque es

muy antiguo y sus respectivas compañías lo han liberado.

Ambos programas son buenos aunque el PALASM no soporta GAL ( Solo PAL)

pero tiene la ventaja de disponer de una herramienta de

simulación. Es solucionarle

porque el OPALJR

lleva un programa para convertir diseños de PAL a diseños

de GAL..

Diseño de la GAL

Para este diseño se necesitaban

10 señales de salida : Fa,

Fb, 8 flip-flop D. Con estos

requerimientos, la GAL a utilizar es la GAL22V10 ( 22 entradas

máximo,10 salidas máximo y con posibilidad de flip-flop

D). El diseño de la GAL con el PALASM se realiza con la

creación de este fichero de texto :

CHIP _gal PAL22V10

En esta parte, indicamos la distribución de

las patillas de la GAL.

;----------------------------------

PIN Declarations ---------------

PIN

1

clk

COMBINATORIAL ;

PIN

2

A0

COMBINATORIAL ;

PIN

3

A1

COMBINATORIAL ;

PIN

4

A2

COMBINATORIAL ;

PIN

5

A3

COMBINATORIAL ;

PIN

6

A14

COMBINATORIAL ;

PIN

7

MERQ

COMBINATORIAL ;

PIN

8

A13

COMBINATORIAL ;

PIN

9

A15

COMBINATORIAL ;

PIN

22..19

Q[3..0]

REGISTERED ;

PIN

17..14

Q[7..4]

REGISTERED;

PIN

18

SA

COMBINATORIAL ;

PIN

23

SB

COMBINATORIAL ;

El pin 1 es obligatoria para el reloj, mientras que

el resto de las patillas las podemos distribuir como queramos. Pines

2,3,4,5,6,7,8,9, son de entrada, pines 18 y 23 son las salidas de las

señales Fa y Fb, Q[3..0] y Q[7..4] representan las salidas con

flip-flop D. La salidas Q[3..0] retorna

internamente para crear las ecuaciones.

;-----------------------------------

Boolean Equation Segment ------

EQUATIONS

SA = A14 + A15 + MERQ

SB = A14 + A15 + MERQ + /A13 +

Q[4] + Q[5] + Q[6] + Q[7]

Q[0] := A2

Q[1] := A1

Q[2] := A3

Q[3] := A0

Q[4] := Q[0]

Q[5] := Q[1]

Q[6] := Q[2]

Q[7] := Q[3]

Se puede ver fácilmente el diseño de

las

salidas en función de las entradas. Se compila resultado un

fichero con extensión *.JED (JEDEC)

que entiende cualquier programados de GAL.

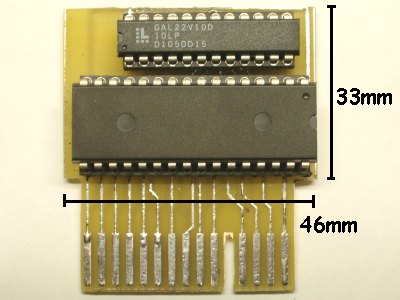

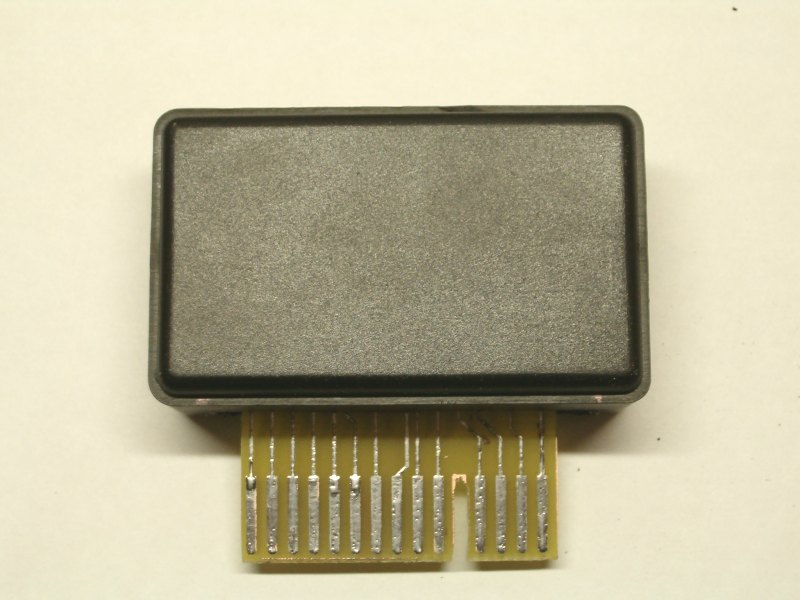

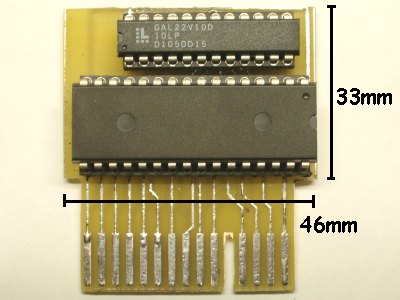

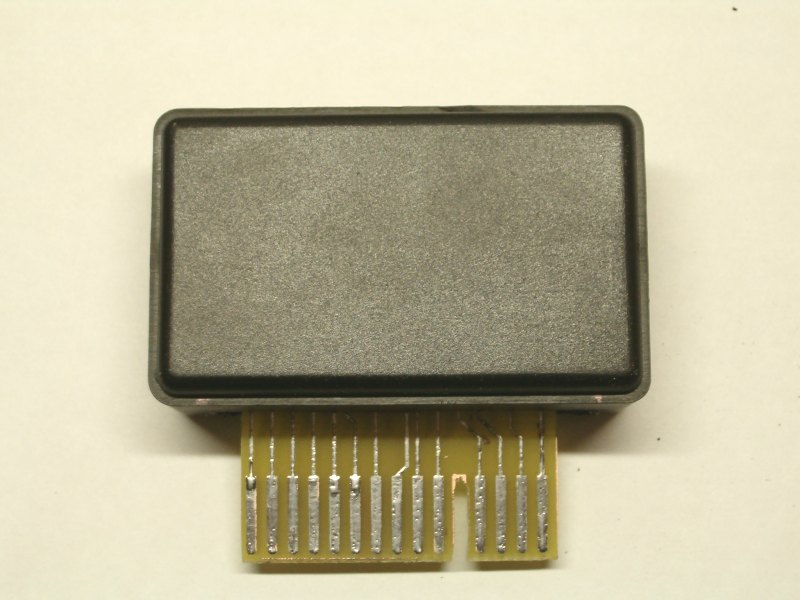

Esquema y placa resultante

La placa resultante es

mucho más pequeña y con menos pistas.

Esta reducción permite meter la placa en una

caja supertronic PP40 y con

algún problema en una PP56 que encaja mejor en el IF2 o

RAM TURBO.

Introducción

Introducción

Diseño con TTL

Diseño con TTL  Diseño con GAL

Diseño con GAL  Funcionamiento y

documentación

Funcionamiento y

documentación

Introducción

Introducción

Diseño con TTL

Diseño con TTL  Diseño con GAL

Diseño con GAL  Funcionamiento y

documentación

Funcionamiento y

documentación